www.afm-iournal.de

# Cubic Phase GaN on Nano-grooved Si (100) via Maskless **Selective Area Epitaxy**

Can Bayram,\* John A. Ott, Kuen-Ting Shiu, Cheng-Wei Cheng, Yu Zhu, Jeehwan Kim, Manijeh Razeghi, and Devendra K. Sadana

A method of forming cubic phase (zinc blende) GaN (referred as c-GaN) on a CMOS-compatible on-axis Si (100) substrate is reported. Conventional GaN materials are hexagonal phase (wurtzite) (referred as h-GaN) and possess very high polarization fields (~MV/cm) along the common growth direction of <0001>. Such large polarization fields lead to undesired shifts (e.g., wavelength and current) in the performance of photonic and vertical transport electronic devices. The cubic phase of GaN materials is polarization-free along the common growth direction of <001>, however, this phase is thermodynamically unstable, requiring low-temperature deposition conditions and unconventional substrates (e.g., GaAs). Here, novel nano-groove patterning and maskless selective area epitaxy processes are employed to integrate thermodynamically stable, stress-free, and low-defectivity c-GaN on CMOScompatible on-axis Si. These results suggest that epitaxial growth conditions and nano-groove pattern parameters are critical to obtain such high quality c-GaN. InGaN/GaN multi-quantum-well structures grown on c-GaN/Si (100) show strong room temperature luminescence in the visible spectrum, promising visible emitter applications for this technology.

#### 1. Introduction

GaN materials (i.e. III-nitrides) are the backbone materials of light emitting diodes (LEDs) emitting in the ultraviolet, blue, and green spectra. LED layers, grown on conventional sapphire and silicon carbide substrates, are hexagonal (i.e. wurtzite) phase and possess inherit polarization fields along the common growth direction <0001>.[1] However, recent studies showed polarization fields to contribute droop phenomena in LEDs<sup>[2]</sup> and I-V hysteresis in resonant tunneling diodes.[3] Thus, it is essential to focus on polarization-free designs to improve GaN photonic and vertical transport device performances.

Conventional approach to enable polarization-free GaN devices is switching the growth plane from inherently polar

C. Bayram, J. A. Ott, K.-T. Shiu, C.-W. Cheng, Y. Zhu, J. Kim, D. K. Sadana IBM Research, Thomas J. Watson Research Center Yorktown Heights, NY 10598, USA E-mail: cbayram@us.ibm.com

M. Razeghi Center for Quantum Devices Department of EECS Northwestern University IL 60208, USA

DOI: 10.1002/adfm.201304062

ones to inherently polarization-free (a.k.a. nonpolar) ones. Practically, most common nonpolar substrate is the m-plane freestanding GaN one (i.e. making 90° with the respect to <0001> direction) that are sliced along {1100} planes out of GaN boules grown along <0001> direction.[4] Hence, m-plane substrates are small area (~cm<sup>2</sup>) and expensive. Moreover, (1) high quality epitaxial regrowth of GaN on nonpolar surfaces is challenging due to low surface energy of nonpolar planes,[5] and (2) indium incorporation into In<sub>x</sub>Ga<sub>(1-x)</sub>N (the visible LED active layers where 0.05 < X < 0.35) is significantly degraded for nonpolar structures<sup>[6]</sup> limiting the promise of such substrates in visible LEDs and laser diodes (LDs) applications.

An alternative way of enabling polarization-free GaN devices is through controlling the material phase. Conventionally-grown GaN material is hexagonal (wurtzite) phase which is polar along

<0001> growth direction. However, GaN material can also be cubic (zinc blende) phase which is polarization-free along <001> growth direction.[7] Nonetheless, cubic phase of GaN is observed to form when grown on cubic substrates such as GaAs. Thermodynamical instability of cubic phase GaN, epilayer-substrate chemical incompatibility (i.e. III-N vs. III-As), and large lattice-mismatch (i.e. ~20%) are some of the key issues bottlenecking such bulk epitaxial deposition schemes.<sup>[8]</sup>

Additional key motivation to our work is the GaN-Si(100) integration that presents further advantages such as on-chip photonics and availability of cleavage. [9,10] However, anisotropic lattice-mismatch (i.e.  $\sim 14\%$  GaN  $< 11\overline{20} > \parallel$  Si  $< \overline{100} >$  and  $\sim 0.6\%$ for GaN<  $10\overline{10}$  >  $\parallel$  Si<  $\overline{100}$  >) and crystallographic asymmetry (i.e. (wurtzite GaN (0001)) six fold versus fourfold (Si(100))) leads to different rotational crystals of GaN grow on Si(100) surface.[11] These lead GaN epilayers suffer from twist boundaries and low quality epitaxy. Thus, offcut-oriented Si(100) substrates (typically 4° to 7° towards (110)) are preferred for single crystalline GaN epitaxy.[12] However, for true integration with silicon electronics, it is essential to develop GaN epitaxy on on-axis Si(100) substrates as offcut in silicon substrates lead to anisotropy and performance issues in silicon electronic devices.[13]

We have addressed such integration issues of GaN on onaxis Si (100) substrates by (1) employing a unique nanopattern on CMOS-compatible Si substrate that expose a U-shaped

ADVANCED FUNCTIONAL MATERIALS

www.afm-journal.de

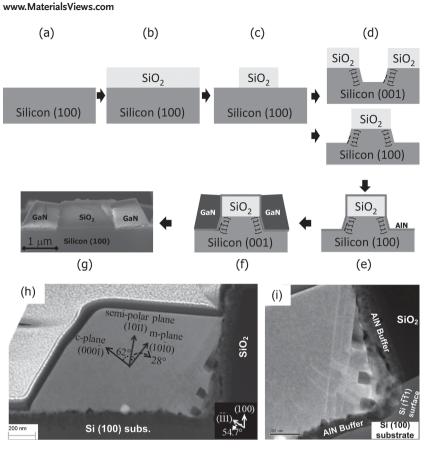

Figure 1. Schematic process flow for (a–d) silicon (100) substrate preparation and (e–f) MOCVD growth processes: (a) RCA cleaning; (b) thermal oxide (SiO<sub>2</sub>) growth; (c) deep ultraviolet (193 nm) lithography and reactive ion etching of oxide (SiO<sub>2</sub>); (d) KOH dip (10%) to create the final groove structures: (top) [SiO<sub>2</sub>-Si{111}-Si{100}-Si{111}-SiO<sub>2</sub>] or (bottom) [SiO<sub>2</sub>-Si{111}-Si{100}]; (e) Low temperature AlN buffer deposition, (f) high temperature GaN layer deposition. (g–i) Cross-section views of wurtzite phase GaN grown: (g) SEM and (h) HAADF-STEM view with crystallographic directions, and (i) HAADF-STEM view zoomed in GaN{000 $\overline{1}$ -Si{ $\overline{111}$ } interface highlighting the stacking faults and dislocation-filtering due to trenched growth mode. The GaN growth is initiated on the exposed Si {111} planes of patterned Si (100) substrate.

groove exposing both Si {111} and Si{100} planes, and (2) developing a truly selective GaN-regrowth scheme that deposits GaN selectively on Si {111} facets rather than Si {100} ones. Besides, a unique phenomenon is observed when two h-GaN growth fronts met in our novel groove structure leading to c-GaN regrowth after seam.

#### 2. Results and Discussion

Figure 1 shows the schematic process flow for silicon (100) substrate preparation prior to MOCVD growth. First, CMOS-compatible on-axis Si (100) substrate is cleaned via standard RCA process. Then, 500-nm-thick thermal oxide (SiO<sub>2</sub>) is grown, followed by deep ultraviolet (193 nm) lithography. Subsequently, reactive ion etching of oxide (SiO<sub>2</sub>) is realized to expose Si (100) surface on parts of the wafer. After another RCA-like cleaning process, the wafer is submersed into KOH (10%) solution for ~1 min to selectively etch Si and expose {111} facet family. By this approach, two different groove

structures  $[SiO_2-Si\{111\}-Si\{100\}]$  and  $[SiO_2-Si\{111\}-Si\{100\}-Si\{111\}-SiO_2]$  are formed on on-axis Si (100) parent substrate, as shown in Figure 1d. After desired groove structures are formed and surface native oxide is removed via dilute HF treatment, wafers are loaded inside the MOCVD chamber for growth.

Figure 1g and Figure 1(h,i) show cross-sectional scanning electron microscope (SEM) and high angle annular dark field (HAADF) scanning transmission electron microscopy (STEM) images of h-GaN, respectively, grown on [SiO<sub>2</sub>-Si{111}-Si{100}] groove structures. The crystallographic directions for h-GaN and Si are displayed in Figure 1h. We have identified the crystallographic directions from the known fact that GaN (0001) growth direction is the same as Si (111) ones, and from our experimental observations that GaN regrowth is nucleated from Si {111} facets only. Given these two, we have used SEM and transmission electron microscope (TEM) to identify the angles between the observed facets of GaN. As wurtzite phase GaN c-plane is along the Si {111}, top GaN facet, making an angle of ~62° and 28° with GaN c- and m-planes, respectively, is determined to be semi-polar ( $10\overline{1}1$ ) plane (see supplementary materials and Figure S1 for crystal directions and planes).[14]

SEM and TEM results show that low temperature (-700 °C) AlN buffer was deposited everywhere (on all Si planes and SiO<sub>2</sub>). This is due to high sticking coefficient of Al adatom and employment of low growth temperatures for the buffer. However, GaN regrowth atop AlN buffer is determined to nucleate from Si( $\overline{111}$ ) surface as shown in

Figure 1i. SEM and TEM are employed to verify that no kind of GaN regrowth or deposition were on the Si {100} facets. This is attributed to optimized MOCVD growth conditions enabling selective nucleation of GaN on Si (111) surfaces rather than Si (100) ones (see supplementary materials and Figures S2–S3). Mainly, our selective MOCVD scheme consists of four steps: (1) Ammonia-free heat up, (2) Prealuminization, (3) AlN buffer deposition, and (4) GaN layer deposition.

Having a  $[SiO_2-Si\{111\}-Si\{100\}]$  trench, GaN growth along the c-direction  $(000\overline{1})$  seems further complicated with void formations. Figure 1i shows the TEM image zoomed in at the GaN-Si interface where partially-filled voids (the dark regions in Figure 1i) and stacking faults (white lines in Figure 1i) along the m-plane  $(\overline{1}0\overline{1}0)$  are observed. Interestingly, as growth front (c-plane) is perpendicular to stacking faults (m-plane), these stacking faults filter the threading dislocations (TDs). Hence, XTEM data reveals no discernable TDs reaching to the topmost GaN surface.

We have further studied the  $GaN\{000\overline{1}\}$ -Si  $\{\overline{11}1\}$  interface to understand mechanisms of such growth selectivity. TEM

www.MaterialsViews.com

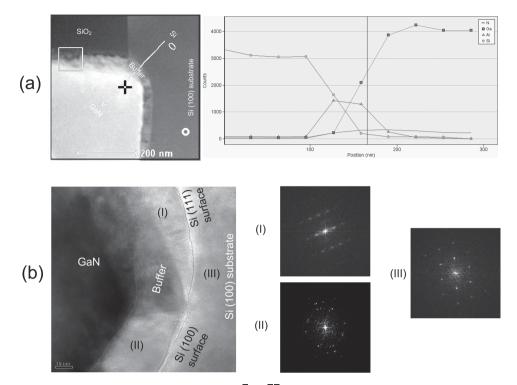

Figure 2. (a) TEM chemical analysis performed through the  $GaN\{000\overline{1}\}$ -Si $\{\overline{1}\overline{1}1\}$  interface (along the red arrow line). Significant Si diffusion into the AIN buffer layer is observed. (b) HR-TEM image of the  $GaN\{000\overline{1}\}$ -Si $\{\overline{1}\overline{1}1\}$  interface interface highlighting a structural difference between the buffer layer on Si (111) and Si (100) surfaces. Red freeform curves are drawn to guide for the buffer layer region. FFT diffraction patterns from selected area regions (I), (II), and (III) are shown (electron beam is parallel to  $[11\overline{2}0]$  zones of h-GaN). Regions (I), (II), and (III) are observed to be wurtzite single crystalline, polycrystalline, and diamond single crystalline.

chemical line and high resolution TEM (HR-TEM) analyses are carried out along the GaN-Buffer-Si interfaces. For buffer layers on Si(111) surfaces, high Si diffusion into the AlN buffer and single crystalline buffer material is observed (see Figure 2). However, for buffer layers on Si(100) surfaces, this was not the case (see supplementary materials and Figure S4). FFT diffraction patterns reveal that the AlN buffer on Si (111) surface is single crystalline in hexagonal (wurtzite) phase whereas that on Si (100) surface is polycrystalline (see Figure 2b). We believe selective GaN growth on Si (111) surfaces is due to this difference in the crystallinity of the corresponding buffer layer.

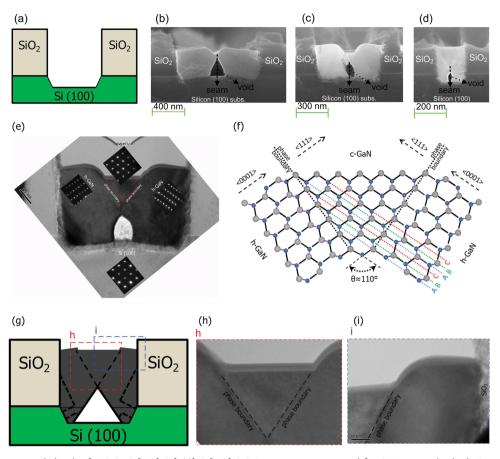

We have then carried out GaN regrowth on [SiO<sub>2</sub>-Si{111}-Si{100}-Si{111}-SiO<sub>2</sub>] groove structures (depicted in **Figure 3a**) under aforementioned selective growth conditions. Such groove structures with short periods are of particular interest to increase effective GaN epitaxial coverage on Si (100) substrate without the expense of growth time as well as may reduce significant wafer bow typically encountered in conventional epitaxy due to the coefficient of thermal expansion (CTE) mismatch between GaN and Si.

Under selective MOCVD growth conditions, GaN regrowth is nucleated on the Si  $\{111\}$  family of planes rather than Si  $\{100\}$  ones, as shown earlier. Thus,  $[SiO_2-Si\{111\}-Si\{100\}-Si\{111\}-SiO_2]$  groove structures have only two nucleation sites for GaN regrowth: Si (111) and Si  $(\overline{111})$ surfaces. When GaN growth fronts initiated from facing directions meet, a void is formed in the middle where the seam forms (Figures 3 and S5).

The size of the void depends on the groove period as well as the growth parameters. [17] Figure 3(b–d) shows the cross-sectional SEM of partially-GaN-filled groove structures with openings of (b) 1000 nm, (c) 650 nm, and (d) 250 nm. Interesting, two distinct features are observed at seam: voids and crystallographic faults.

Figure 3 shows the bright-field TEM of a groove structure. Figure 3h shows bright-field TEM image zoomed around the seam area. These TEM data shows that some intersecting crystallographic faults are initiated at seam forming a triangular region (see Figure 3f for the exploratory sketch and supplementary materials for Figure S6). To understand the nature of such faults, Fast Fourier transform (FFT) technique is employed to check and determine GaN crystalline phase inside and outside the triangular region.

Selective area electron diffraction patterns are shown in Figure 3e. Diffraction patterns from the exact regions and the orientation of the sample have been maintained. These different diffraction patterns correspond to wurtzite and cubic phase crystallographic electron diffractions of GaN, respectively, given that the TEM data was taken with electron beam parallel to [1120] zone of wurtzite phase GaN (that corresponds to [110] zone of cubic phase GaN) (see Figure S7). [18,19] Thus, crystallographic faults initiated at the seam are identified to be phase boundaries. Bright-field TEM images in Figure 3 reveal no threading dislocations on both c-GaN and h-GaN surfaces. Authors believe phase boundaries circumscribing the cubic phase GaN (V-shape alike) help suppress

ADVANCED FUNCTIONAL MATERIALS

www.afm-journal.de

Figure 3. (a) Cross-sectional sketch of a  $[SiO_2-Si\{111\}-Si\{100\}-Si\{110\}-Si\{111\}-SiO_2]$  groove structure used for GaN regrowth. (b–d) Cross-sectional SEM of GaN grown on grooved Si (100) substrate having openings of (b) 1000 nm, (c) 650 nm, and (d) 250 nm. (e) Cross-sectional bright-field TEM of a partially-GaN-filled groove structure. FFT diffraction patterns of boxed regions shown correspond to c-GaN, h-GaN, and Si (100) (see supplementary materials). Diffraction patterns from the exact regions and the orientation of the sample have been maintained. Electron beam is parallel to  $[11\overline{2}0]$  and  $[1\overline{1}0]$  zones of wurtzite and cubic phase GaN, respectively. (f) Cross-sectional sketch depicting wurtzite to cubic phase transition observed in the groove. (g) Cross-sectional sketch of a partially-GaN-filled groove structure. (h,i) Bright-field TEM images of (h) c-GaN and (i) h-GaN surfaces revealing no threading dislocations.

TDs propagation as cubic phase growth front is aligned with Si[100] direction whereas wurtzite phase growth front is aligned with Si[111].

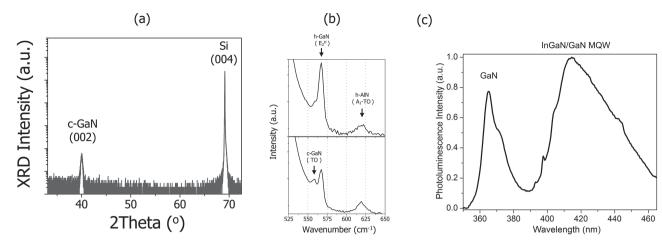

X-ray diffraction (XRD) studies are carried out to verify the phase of GaN grown on [SiO<sub>2</sub>-Si{111}-Si{100}-Si{111}-SiO<sub>2</sub>] groove structure. Omega/2Theta XRD data shown in Figure 4a reveals a peak at ~40° corresponding to the cubic phase of GaN. Room temperature Micro-Raman measurements are carried out for GaN on on [SiO<sub>2</sub>-Si{111}-Si{100}] and [SiO<sub>2</sub>-Si{111}-Si{100}-Si{111}-SiO<sub>2</sub>] groove structures (see Figure 4b). We observed only h-GaN peak for the former whereas the latter showed a c-GaN peak as well. Interestingly, comparing the Raman peak locations of h-GaN and c-GaN on grooved Si (100) with the literature, [20,21] one can conclude that these materials are stress-free (freestanding GaN Micro-Raman spectrum provided in Figure S9). Authors believe this is due to the localized epitaxy process rather than conventional bulk deposition.

As XTEM data identified no discernable TDs reaching to the cubic-phase GaN surface, we have grown three period InGaN/GaN multi-quantum-well (MQW) active layer on such cubic phase GaN on [SiO $_2$ -Si{111}-Si{100}-Si{111}-SiO $_2$ ] groove

Adv. Funct. Mater. 2014, 24, 4492-4496

structures. Figure 4(c) shows the room temperature photoluminescence (PL) measurement data. Intense ultraviolet and blue luminescence are observed from GaN and InGaN/GaN MQW, respectively, proving the optical quality of the regrown layers on cubic phase GaN.

### 3. Conclusions

CMOS-compatible integration of wurtzite and cubic phase GaN on on-axis Si (100) substrates are realized through novel nano-groove pattern and selective MOCVD process. XTEM data shows no discernable threading dislocations on the h- and c-GaN surfaces. InGaN/GaN MQWs regrown on c-GaN templates demonstrated strong room temperature emission in blue spectrum. GaN wurtzite to cubic phase transition can be particularly beneficial for light emitting devices as GaN cubic phase is nonpolar and polarization-free. Our MOCVD growth technique and unique groove structure are particularly beneficial for integrating GaN devices with Si CMOS technology (see Figure S9).

www.MaterialsViews.com

Figure 4. (a) Omega/2Theta XRD scan of GaN on a [SiO<sub>2</sub>-Si{111}-Si{100}-Si{111}-SiO<sub>2</sub>] groove structure showing cubic phase diffraction peak. (b) Room temperature Micro-Raman spectra of (top) GaN on [SiO<sub>2</sub>-Si{111}-Si{100}] groove structure (seen in Figure 1(h)) and (bottom) GaN on a [SiO<sub>2</sub>-Si{111}-Si{100}-Si{111}-SiO<sub>2</sub>] groove structure (seen in Figure 3(e)). The former has only h-GaN whereas the latter shows additional c-GaN peak. (c) Room temperature PL spectrum of InGaN multi-quantum-wells grown on GaN on a [SiO2-Si{111}-Si{100}-Si{111}-SiO2] groove structure. Strong ultraviolet and blue luminescence are observed from GaN and InGaN/GaN multi-quantum-wells, respectively.

## 4. Experimental Section

Our optimal MOCVD condition consists of a four step approach: (1) Ammonia-free heat up (~5-10 min) to prevent Si surface nitridation and remove any native oxide, (2) long-enough prealuminization via introducing only TMAI into the chamber to aluminize the Si surface (at least 10 s) prior to any deposition, (3) thick-enough AIN buffer deposition (at least 60-nm-thick deposited at 700 °C) prior to GaN deposition, and (4) high temperature GaN regrowth (at a temperature of ≥1150 °C). Such optimized MOCVD parameters enable a uniform and controlled GaN regrowth (Figure S2 right) over that under conventional conditions (Figure S2 left).

## Acknowledgments

Dr. Bayram acknowledges valuable collaboration with Center for Quantum Devices of Northwestern University, Evanston, USA. The authors would like to thank Drs. G. Shahidi and T. C. Chen for their encouragement and support of this work.

> Received: December 3, 2013 Revised: February 11, 2014 Published online: April 1, 2014

- [1] F. Bernardini, V. Fiorentini, D. Vanderbilt, Phys. Rev. B 1997, 56, R10024-R10027.

- [2] G. Verzellesi, D. Saguatti, M. Meneghini, F. Bertazzi, M. Goano, G. Meneghesso, E. Zanoni, J. Appl. Phys. 2013, 114, 071101.

- [3] C. Bayram, Z. Vashaei, M. Razeghi, Appl. Phys. Lett. 2010, 97, 181109.

- [4] J. S. Speck, S. F. Chichibu, MRS Bull. 2009, 34, 304-309.

- [5] Q. Sun, C. D. Yerino, B. Leung, J. Han, M. E. Coltrin, J. Appl. Phys. **2011**, 110, 053517.

- [6] Y. Zhao, Q. Yan, C.-Y. Huang, S.-C. Huang, P. S. Hsu, S. Tanaka, C.-C. Pan, Y. Kawaguchi, K. Fujito, C. G. Van de Walle, J. S. Speck, S. P. Denbaars, S. Nakamura, D. Feezell, Appl. Phys. Lett. 2012, 100,

- [7] O. Ambacher, J. Phys. D: Appl. Phys. 1998, 31, 2653-2710.

- [8] S. V. Novikov, N. M. Stanton, R. P. Campion, R. D. Morris, H. L. Geen, C. T. Foxon, A. J. Kent, Semicond. Sci. Technol. 2008, 23, 015018

- [9] III-V Compound Semiconductors: Integration with Silicon-Based Microelectronics (Eds: T. Li, M. Mastro, A. Dagar), CRC Press, Florida, USA 2010, Chapter 3.

- [10] A. Dadgar, F. Schulze, M. Wienecke, A. Gadanecz, J. Bläsing, P. Veit, T. Hempel, A. Diez, J. Christen, A. Krost, New J. Phys. 2007, 9, 389.

- [11] P. A. Larssen, Acta Cryst. 1996, 20, 599.

- [12] F. Schulze, A. Dadgar, J. Bläsing, T. Hempel, A. Diez, J. Christen, A. Krost, J. Cryst. Growth 2006, 289, 485-488.

- [13] A. J. Hughes, A. C. Thorsen, J. Appl. Phys. 1973, 44, 2304-

- [14] F. Scholz, Semicond. Sci. Technol. 2012, 27, 024002.

- [15] L. Lee, K.-F. Chien, W.-C. Chou, C.-H. Ko, C.-H. Wu, Y.-R. Lin, C.-T. Wan, C. H. Wann, C.-W. Hsu, Y.-F. Chen, Y.-K. Su, Cryst. Eng. Comm. 2012, 14, 4486.

- [16] C. J. M. Stark, T. Detchprohm, S. C. Lee, Y.-B. Jiang, S. R. J. Brueck, C. Wetzel, Appl. Phys. Lett. 2013, 103, 232107.

- [17] S. C. Lee, X. Y. Sun, S. D. Hersee, S. R. J. Brueck, J. Cryst. Growth **2005**, 279, 289-292.

- [18] Y. Cui, V. K. Lazorov, M. M. Goetz, H. Liu, D. P. Robertson, M. Gajdardziska-Josifovska, L. Li, Appl. Phys. Lett. 2003, 82, 4666-4668

- [19] S. C. Lee, X. Y. Sun, S. D. Hersee, S. R. J. Brueck, H. Xu, Appl. Phys. Lett. 2004, 84, 2079-2081.

- [20] H. Morkoc, Handbook of Nitride Semiconductors and Devices, Volume 1, Wiley, Germany 2008.

- [21] X. L. Sun, H. Yang, L. X. Zheng, D. P. Xu, J. B. Li, Y. T. Wang, G. H. Li, Z. G. Wang, Appl. Phys. Lett. 1999, 74, 2827-2829.